# Design Methodology and Implementation of Fully Passive RFID SoC with Temperature Sensor

#### Jun Tan

Supervisor: Univ.-Prof. Dr.-Ing. Ralf Sommer

Advisor: Prof. Dr.-Ing. Eckhard Hennig Prof. Dr.-Ing. Klaus Hofmann

Department of Electrical Engineering and Information

Technology

Technische Universität Ilmenau

This dissertation is submitted for the degree of *Doktor-Ingenieur*November 14, 2019

urn:nbn:de:gbv:ilm1-2021000053

## **Abstract**

This dissertation presents the methodology and implementation of a fully passive RFID SoC with temperature sensor to reduce supply noise for high accurate wireless temperature measurement. The analysis of the state-of-the-art standalone temperature sensors and the RFID wireless temperature sensors reveals a design challenge that the RFID sensors suffer significantly from the supply noise, due to the RFID communication. In order to improve sensor accuracy without making too many compromises, this dissertation presents the following scientific contributions. First, a time-domain low-voltage low-power temperature sensor is proposed to achieve high accuracy without using a highly complex  $\Sigma\Delta$  ADC with low sampling rate . In addition, the methodology for the analysis of supply noise is developed for the generation, the amplification and the digitization of the supply noise. The analysis results show that the supply noise is distributed over a wide frequency spectrum, while the noise in the communication frequency band is amplified by the power management unit. For the analysis of noise digitization by the sensors, this proposed temperature sensor achieves the best-in-class DC supply sensitivity while it still suffers from AC ripple. Therefore, the supply noise generated by RFID communication will significantly affect the sensor performance. The final optimization at system level is achieved by introducing a serial readout command that significantly reduces the supply noise for the sensor readout. The experimental results show that this proposed RFID temperature sensor achieves  $\pm 0.4$  °C (3 $\sigma$ ) from 0 °C to 125 °C,

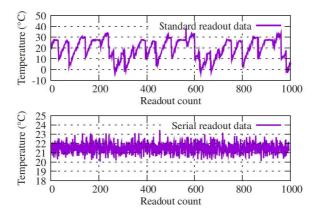

which is the highest accuracy with the largest operational range compared to the currently reported state-of-the-art RFID temperature sensors. The new RFID command improves the resolution of this RFID temperature sensor by a factor of 16.

# Kurzdarstellung

Diese Dissertation stellt die Methodik und die Implementierung eines vollständig passiven RFID SoC mit Temperatursensor zur Reduzierung von Versorgungsrauschen für eine hochgenaue drahtlose Temperaturmessung vor. Die Analyse der modernen eigenständigen Temperatursensoren und der drahtlosen RFID Temperatursensoren zeigt eine Design Herausforderung, dass die RFID Sensoren aufgrund der RFID Kommunikation erheblich unter dem Versorgungsrauschen leiden. Um die Sensorgenauigkeit zu verbessern, ohne zu viele Kompromisse einzugehen, stellt diese Dissertation die folgenden wissenschaftlichen Beiträge vor. Zuerst wird ein Zeitdomain Niederspannungs Niederleistungs Temperatursensor vorgeschlagen, um eine hohe Genauigkeit zu erreichen, ohne einen hochkomplexen  $\Sigma\Delta$  ADC mit niedriger Abtastrate zu verwenden. Darüber hinaus wird die Methodik zur Analyse von Versorgungsrauschen für die Erzeugung, Verstärkung und Digitalisierung des Versorgungsrauschens entwickelt. Die Analyseergebnisse zeigen, dass das Versorgungsrauschen über ein breites Frequenzspektrum verteilt ist, während das Rauschen im Kommunikationsfrequenzband durch das Power Management Unit verstärkt wird. Für die Analyse der Rauschdigitalisierung erreicht dieser vorgeschlagene Temperatursensor die beste DC Versorgungsempfindlichkeit seiner Klasse, während er noch unter Wechselstromwelligkeit leidet. Daher wird das durch die RFID Kommunikation erzeugte Versorgungsrauschen die Sensorleistung erheblich beeinflussen. Die abschließende Optimierung auf Systemebene wird durch die Einführung

eines seriellen Auslesekommandos erreicht, das das Versorgungsrauschen für die Sensorauslesung deutlich reduziert. Die experimentellen Ergebnisse zeigen, dass dieser vorgeschlagene RFID Temperatursensor die Genauigkeit von  $\pm 0.4\,^{\circ}\mathrm{C}$  (3 $\sigma$ ) von 0 °C bis 125 °C erreicht. Die ist höchste Genauigkeit mit der größten Arbeitsbereich im Vergleich zu den derzeit berichteten modernen RFID Temperatursensoren. Der neue RFID Befehl verbessert die Auflösung dieses RFID Temperatursensors um den Faktor 16.

## **Preface**

My motivation to solve analog design problems always drives me to analyze the crucial factor of the problem, to develop a better topology and to push the performance to its limits. The present work is a compilation of the results and insights collected during my time at IMMS Institut für Mikroelektronik- und Mechatronik-Systeme gemeinnützige GmbH (IMMS GmbH), Ilmenau, Germany. With a working atmosphere of open, support and fun, the ideas of this dissertation have been slowly but fully developed, implemented and tested.

My research was part of three projects. The *GreenSense* [62] project has been funded by the "Land" of Thüringen (Ministry of Economics, Labour and Technology) and the European Social Fund (ESF) under the reference 2011 FGR 0121. The *ADMONT* [61] project has received funding from the ECSEL Joint Undertaking under grant agreement No 661796. This Joint Undertaking has received support as Innovation Action from the European Union's Horizon 2020 research and innovation programme, the German Federal Ministry of Education and Research (BMBF) and Finland, Sweden, Italy, Austria, Hungary. The IMMS sub-project "Design of intelligent in vitro diagnostic und bioanalytical sensor and actuator system" has received funding under the reference 16ESE0057. The *RoMulus* [63] project is supported within the Research Programme ICT 2020 by the German Federal Ministry of Education and Research (BMBF) under the reference 16ES0362.

I thank the director of the institute, Prof. Ralf Sommer, for the opportunity to work under his supervision and for the freedom to develop my own ideas. Furthermore, I am grateful to Prof. Eckhard Hennig for the inspiring and fruitful discussions during the GreenSense project and for reviewing my thesis. I also thank Prof. Klaus Hoffman for reviewing my thesis.

Several people have supported me significantly during this thesis. I would like to thank: my design partner M.Sc. Muralikrishna Sathyamurthy for the digital design; my laboratory mate Dipl. -Ing. Alexander Rolapp for the measurement; M.Sc. Jonathan Gamez, M.Sc. Moataz Elkharashi and M.Sc. Thanuchith Vakkaliga Raju for the design support; head of the microelectronic department M.Sc. Eric Schäfer for both scientific and administrative matters; all other colleagues for the pleasant working atmosphere.

I thank Prof. R. Sommer, Prof. E. Hennig, Dr. -Ing. Dominik Krauße and M.Sc. E. Schäfer for proof-reading my thesis.

Finally, I thank my parents, my wife Qiong and my both boys Lukas and Julian for their understanding and encouragement for my work and my life.

Jun Tan Erfurt, 26th September 2019

# **Table of contents**

| 1 | Intr | oductio | n                                                 | 1  |

|---|------|---------|---------------------------------------------------|----|

|   | 1.1  | Radio   | Frequency Identification (RFID)                   | 1  |

|   | 1.2  | High-c  | lensity multi-mode RFID smart sensor network      | 3  |

|   | 1.3  | Techno  | ology overview and related state-of-the-art works | 5  |

|   | 1.4  | Task d  | efinition and proposal of this thesis             | 13 |

|   | 1.5  | Structu | are of this thesis                                | 15 |

| 2 | Desi | on metl | hodology of supply noise analysis                 | 17 |

| = | 2.1  | _       | action                                            |    |

|   | 2.2  |         |                                                   |    |

|   |      |         | ation of the supply noise                         |    |

|   | 2.3  | Ampli   | fication of the supply noise                      |    |

|   |      | 2.3.1   | Problem identification                            | 24 |

|   |      | 2.3.2   | Modeling implementation                           | 25 |

|   |      | 2.3.3   | Transfer function calculation                     | 27 |

|   |      | 2.3.4   | Modeling verification                             | 34 |

|   |      | 2.3.5   | Methodology for LDO PSR optimization              | 38 |

|   | 2.4  | Time-c  | domain temperature sensor topology                | 44 |

|   |      | 2.4.1   | Overview of voltage-domain temperature sensors    | 44 |

|   |      | 2.4.2   | Conversion of voltage-domain to time-domain       | 47 |

|   |      | 2.4.3   | Sensor modeling                                   | 49 |

|   |      | 2.4.4   | Parameter selection and model verification        | 53 |

x Table of contents

|   | 2.5 | Digitization of the supply noise and comparison 5          | 9  |

|---|-----|------------------------------------------------------------|----|

|   |     | 2.5.1 Modeling of the state-of-the-art sensor topologies 5 | 9  |

|   |     | 2.5.2 Time-domain temperature sensor topology analysis 6   | 7  |

|   | 2.6 | Summary                                                    | 13 |

| _ |     |                                                            | _  |

| 3 |     | 6                                                          | 15 |

|   | 3.1 |                                                            | 5  |

|   | 3.2 |                                                            | 6  |

|   |     |                                                            | 6  |

|   |     | 7 6                                                        | 31 |

|   |     | 3.2.3 Top level of the test chip                           | 32 |

|   |     | 3.2.4 Experimental results                                 | 34 |

|   | 3.3 | RFID implementation                                        | 8  |

|   |     | 3.3.1 PMU implementation                                   | 88 |

|   |     | 3.3.2 RFID frontend implementation                         | 2  |

|   |     | 3.3.3 RFID simulation results                              | 15 |

|   | 3.4 | Summary                                                    | 1  |

| 4 | C4  |                                                            | 12 |

| 4 | 7.  | em integration and physical design                         |    |

|   | 4.1 | Introduction                                               |    |

|   | 4.2 | System level optimization                                  |    |

|   |     | 4.2.1 Communication protocol                               |    |

|   |     | 4.2.2 Serial readout command                               |    |

|   | 4.3 | System integration                                         | 8  |

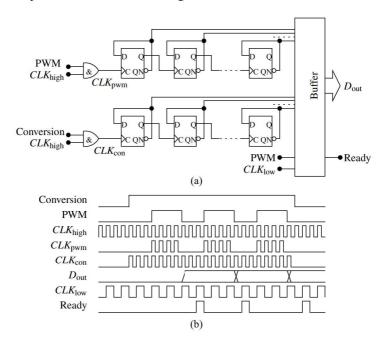

|   |     | 4.3.1 Time-to-digital converter                            | 8  |

|   |     | 4.3.2 Digital control logic                                | 0  |

|   |     | 4.3.3 System schematic                                     | 0  |

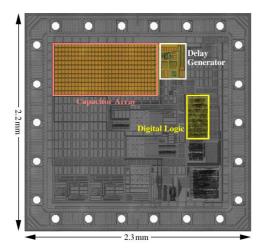

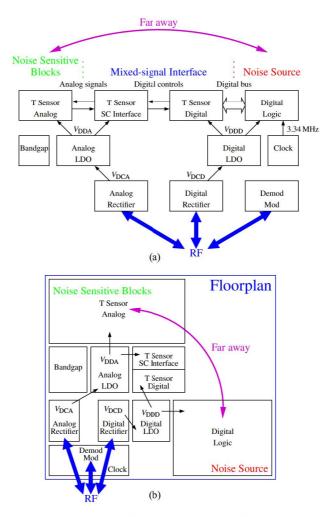

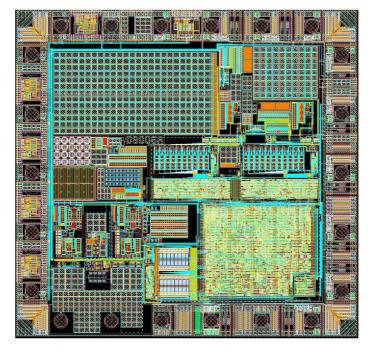

|   | 4.4 | Physical design                                            | 1  |

|   |     | 4.4.1 Floorplan                                            | 2  |

|   |     | 4.4.2 Final layout                                         | 4  |

|   | 45  | Summary 11                                                 | 5  |

Table of contents xi

| 5 | Exp  | erimental results                                          | 117 |

|---|------|------------------------------------------------------------|-----|

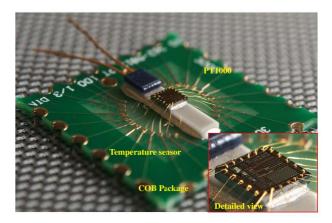

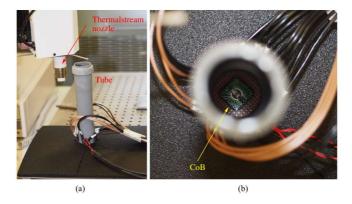

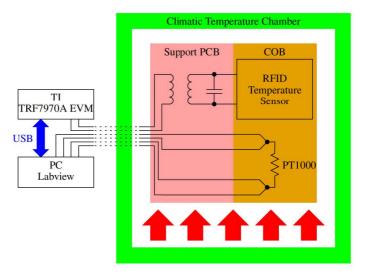

|   | 5.1  | Measurement setup                                          | 117 |

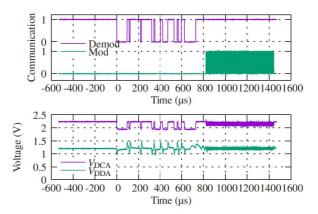

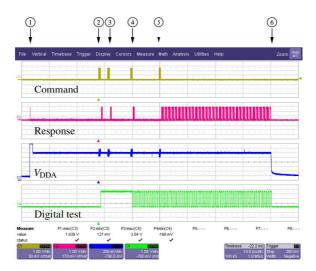

|   | 5.2  | RFID communication & PMU characterization                  | 121 |

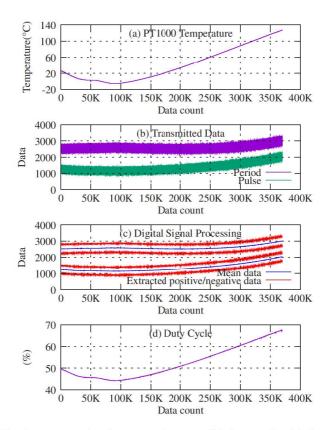

|   | 5.3  | Wireless sensor characterization                           | 124 |

|   |      | 5.3.1 Accuracy characterization                            | 125 |

|   |      | 5.3.2 Noise characterization                               | 128 |

|   | 5.4  | Performance comparison with state-of-the-art RFID tempera- |     |

|   |      | ture sensors                                               | 129 |

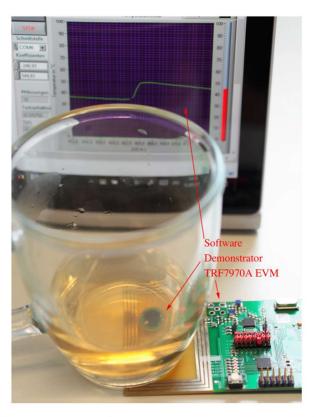

|   | 5.5  | Demonstrator                                               | 131 |

| 6 | Sum  | nmary and outlook                                          | 133 |

| 7 | Zusa | ammenfassung und Ausblick                                  | 137 |

# **Chapter 1**

## Introduction

#### 1.1 Radio Frequency Identification (RFID)

Remote identification and control of the objects without physical contact was first introduced during World War II [39]. After thirty years, this advanced military technology is started to be used in civilian applications [22]. In the 21st century, this Radio-frequency identification (RFID) technology [1] exploded and became part of everyday life. Today, RFID is evolving in even more areas, bringing wireless connectivity to millions and millions objects.

The typical RFID system consists of an interrogator (reader), a transponder (tag) and a server (data processing). The RFID tag is a tiny integrated circuit with an antenna. The RFID reader queries tags for information stored on them. This information can be their static identification numbers or user defined data. The server processes the data obtained from the readers.

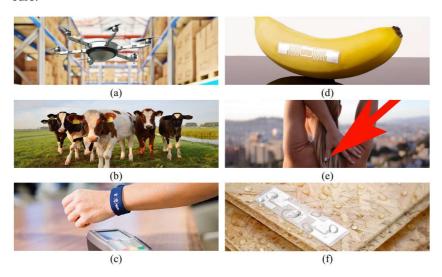

The traditional applications of RFID are access control and asset tracking in manufacturing, retail and logistics businesses. Recently, these application scenarios have been extended to the area that has never been so large before. In [70] (Fig. 1.1 (a)), MIT researchers are developing a system that enables

drones to read RFID tags from a relatively long distance while identifying and locating the objects. The technology can be used in large warehouses to continuously monitor and locate individual items to prevent inventory mismatches. In [68] (Fig. 1.1 (b)), cattle tracking using RFID has been approved by the U.S. Department of Agriculture (USDA) in conjunction with the agency's Animal Identification Number (AIN) system. In [75] (Fig. 1.1 (c)), the payment RFID wristband enables contactless and cashless payment that is simple, fast and secure.

Fig. 1.1 The application scenario of RFID is widely expanded.

Passive RFID sensor tags have attracted increasing attention in the last decade. With energy harvesting, RFID communication and sensor functionality, passive RFID sensor tags are suitable for a wide range of applications involving Wireless Sensor Networks (WSN) and the Internet of Things (IoT) [35, 59].

In [71, 56] (Fig. 1.1 (d)), food safety can be tested by changing from the wireless signals emitted by RFID tags when the signals interact with food. The technology can prevent food contamination without modifying the current

RFID tag hardware. In [57] (Fig. 1.1 (e)), the UV light can be detected by a tiny RFID sensor that can be affixed to the thumbnail. The sensor readout is accomplished by the NFC enabled smart phones. In [79] (Fig. 1.1 (f)), the moisture condition can be measured with a UHF RFID tag in harsh industrial environments such as construction, energy, healthcare, automotive production and military.

# 1.2 High-density multi-mode RFID smart sensor network

The vision of the application scenario [62] of this dissertation is based on discussions with local companies and research institutes to develop an innovative sensor solution for the market expansion of bioanalytics and medical diagnostics. In the bioanalytics and medical engineering, there is a growing need for sensors that require rapid fluid analysis and long-term monitoring of patient vital function.

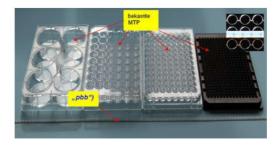

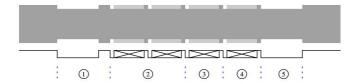

Fig. 1.2 Microtiter plates for the bioanalytics [65]

Fig. 1.2 shows an example of microtiter plates (MTP) in bioanalytics for parallel analysis of a large number of individual samples (e.g. cell cultures). The goal is simultaneous, contamination-free acquisition of various physical and chemical parameters in extremely dense arrays of liquid samples with RFID

micro-sensors (see Fig. 1.3). This results in the following general requirements for the sensors and the sensor network:

Fig. 1.3 Rapid analysis of liquid samples in microplates [62].

- Extreme miniaturization of the sensor nodes, whose permissible size is limited by the size of the sample container,

- Multi-mode integrated Smart Sensor, such as temperature, pH-value, and turbidity etc,

- Contact-less power supply and data transmission (e.g. via RFID),

- Extremely low power consumption to avoid heat transfer to samples,

- Very fast addressing and reading of a complete array of several hundred samples,

- Low manufacturing cost per sensor unit.

## 1.3 Technology overview and related state-of-theart works

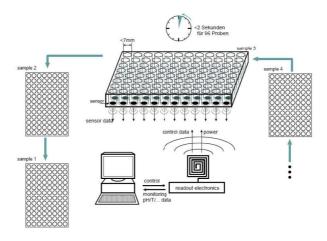

This dissertation utilises several technologies to address the challenges. Many of them have been further developed and improved. The technology map is shown in Fig. 1.4. In the following sections, some important technologies are introduced in detail.

Fig. 1.4 Technology map of this dissertation

#### **Design methodology**

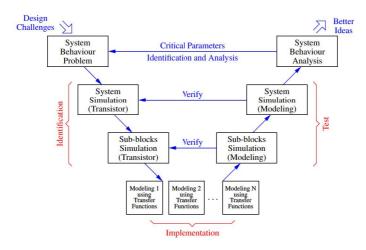

The V-diagram [83] is a graphical representation of a system development life cycle and it is widely applied in software development. It is also widely used for design methodology in analog and mixed-signal application specific integrated circuit (ASIC) designs.

On the left, the design is a top-down approach. In this approach, the overview of the system is first formulated and specified, without details. With the design goes to a deeper level, the details are revealed in the sub-systems. On the right,

verification is a bottom-up approach. In contrast to the design phase, verification begins at a lower level in the individual sub-systems. If the system fails verification, the design is reinitialized at the same level for further iteration.

Fig. 1.5 The V diagram [83] is originally used in software development. It is also used in the ASIC designs.

#### Low-power temperature sensor

CMOS on-chip temperature sensors are being widely adopted for applications that require highly accurate and energy efficient cost-effective solutions for temperature acquisition. These include low-power sensing applications in biomedical, life science, and logistics fields.

According to recent temperature sensor survey [69, 49], CMOS on-chip temperature sensors can be categorized into three major types.

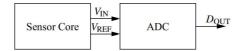

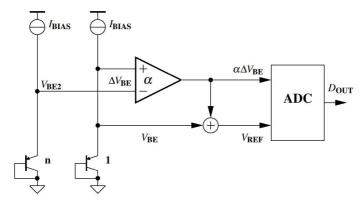

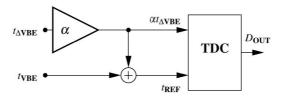

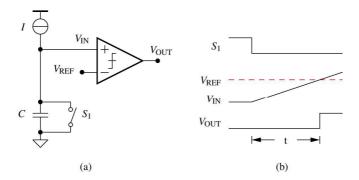

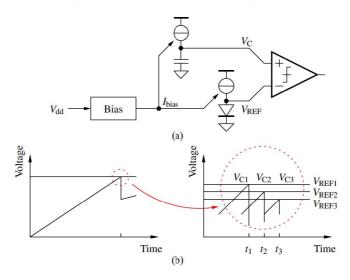

Voltage-domain sensors use a temperature-dependent voltage source and a voltage ADC to convert a temperature signal into a digital code, e.g. [31, 37]. In Fig. 1.6, the sensor core generates two voltages: temperature dependent  $V_{\rm IN}$  and temperature independent  $V_{\rm REF}$ . The ADC evaluates  $V_{\rm IN}$  using the reference voltage  $V_{\rm REF}$  and generates the digital code  $D_{\rm OUT}$ .

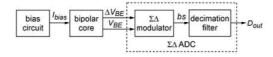

In [31], the topology is improved by a bias circuit, a bipolar core and a  $\Sigma\Delta$  ADC (Fig. 1.7). The voltages  $\Delta V_{BE}$  and  $V_{BE}$  are both temperature dependent,

Fig. 1.6 The block diagram of a voltage-domain temperature sensor.

while the reference voltage is built inside the  $\Sigma\Delta$  ADC using switched-capacitor circuits. The design utilizes complex ADC topology and design techniques to achieve a high accuracy of  $\pm 0.1$  °C (3 $\sigma$ ) in a wide temperature range (–55 °C to 125 °C). On the other hand, the design consumes 75  $\mu A$  under 2.5 V supply voltage in a 0.7  $\mu m$  CMOS technology. Due to the "incremental" natural of the  $\Sigma\Delta$  ADC, a single 16-bit digital output can only be generated after several hundred clock cycles, so the conversion time of this design reaches only 100 ms. The supply sensitivity is 0.03 °C/V.

Fig. 1.7 Block diagram of the voltage-domain temperature sensor [31].

In [37], the design is improved by a zoom ADC that combines SAR and  $\Delta\Sigma$  principles. A high accuracy up to  $\pm 0.15$  °C was achieved in a temperature range from -55 °C to 125 °C with a power dissipation of  $5.1 \,\mu\text{W}$ . Compared to [31], the conversion time is improved to  $5.3 \,\text{ms}$ , while the supply sensitivity is punished to  $0.5 \,$  °C/V.

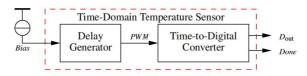

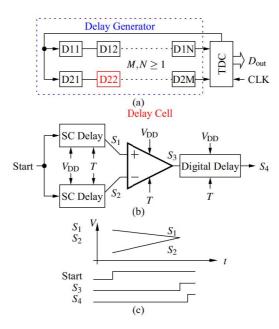

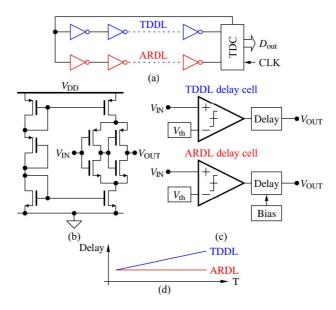

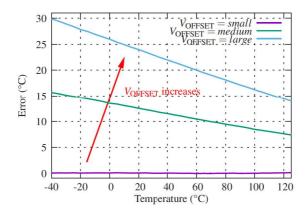

*Time-domain* temperature sensors [32] consists of a temperature-to-pulse generator (delay generator) and a time-to-digital converter (TDC). The delay generator generates a digital pulse with a temperature-dependent delay, e.g. [32, 23, 12, 52]. The time-to-digital converter (TDC), which can be implemented with a simple digital counter, measures the delay and generates a corresponding output code. Fig. 1.8 shows the typical topology of time-domain temperature

sensor. The delay generator is normally implemented by SC circuits [23] or inverters [32, 12, 52].

Fig. 1.8 Block diagram of the time-domain temperature sensor [32].

In [12], an inverter-based delay generator in [32] is improved with SAR logic to achieve an inaccuracy of  $-0.4\,^{\circ}\text{C}$  to  $0.6\,^{\circ}\text{C}$  from  $0\,^{\circ}\text{C}$  to  $90\,^{\circ}\text{C}$  after a two-point calibration. The average power dissipation of the sensor is  $36.7\,\mu\text{W}$  with a conversion rate of 2 Samples/s.

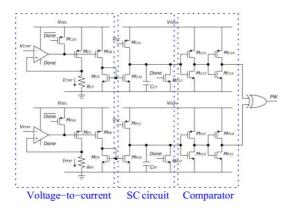

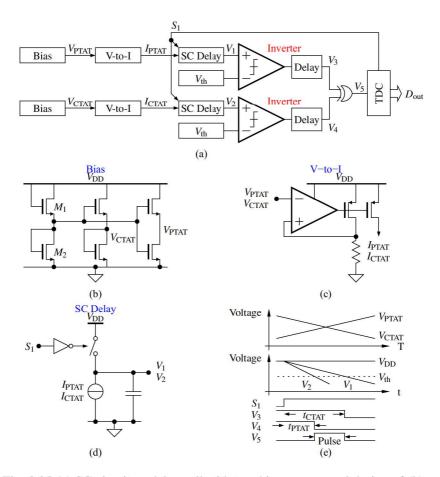

[23] introduces an ultra-low-power (ULP) on-chip CMOS temperature sensor with simple structure. In Fig. 1.9, the delay generator is composed of voltage-to-current (V-to-I) converters, SC circuits and inverter-based comparators. The temperature-dependent bias voltages  $V_{\rm PTAT}$  and  $V_{\rm CTAT}$  are converted into temperature-dependent bias currents in the V-to-I converters. The current discharges the voltages of the SC circuit, after the capacitor is reset to the supply voltage. The inverter-based comparator compares the SC voltage to its own threshold voltage to generate the timing signal. The proposed temperature sensor with 100 nW and 25 Samples/s was reported. It achieves an inaccuracy of  $-0.8\,^{\circ}\text{C}$  to  $1\,^{\circ}\text{C}$  from  $-10\,^{\circ}\text{C}$  to  $30\,^{\circ}\text{C}$  with a sampling rate of 33 Samples/s. The main challenge of this topology is that the inverter-based comparator has a various threshold voltage due to the process-voltage-temperature (PVT) variation. The SC circuit is bound to the supply voltage during the reset phase, so that it is also sensitive to the supply voltage variation. Due to its narrow temperature range, it is restricted to a small range of applications.

The third class of temperature sensors operates in the *frequency domain*, e.g. [16, 18]. They use similar structures as the previous type but deliver

Fig. 1.9 Block diagram of the delay generator in [23].

temperature-dependent frequencies. The sensor reported in [16] achieves -1.6/3 °C inaccuracy in the range from 0 °C to 100 °C and consumes 200 nW.

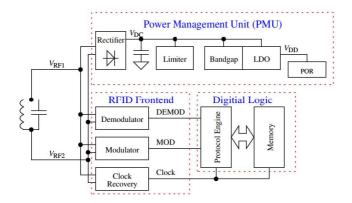

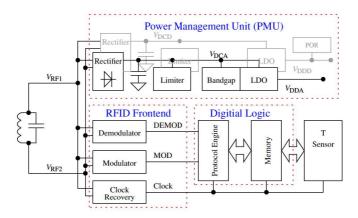

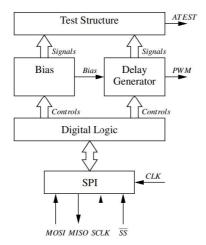

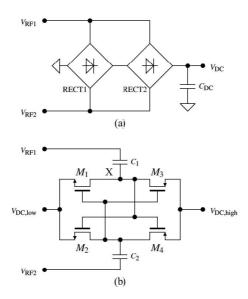

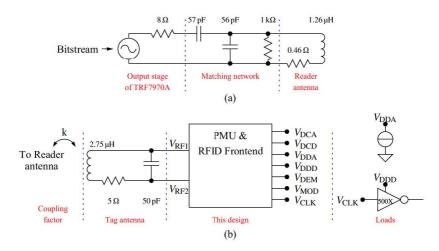

#### RFID sensor tag

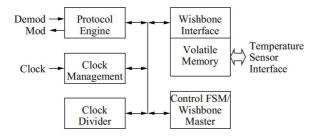

The conventional RFID architecture consists of a Power Management Unit (PMU), a RFID frontend, and digital logic (Fig. 1.10). The PMU harvests the RF field energy and converts it to the DC voltage  $V_{\rm DC}$ . Further they are regulated supply voltages  $V_{\rm DD}$  for the chip. The rectifiers, the bandgap, and the low-dropout regulators (LDO) form the main power path. The power limiter limits the voltage when the incoming power is too high. The power-on reset (POR) circuit generates the reset signal during start-up. The RFID frontend consists of a demodulator, a modulator, and a clock recovery circuit [13, 24]. The demodulator converts the modulated RF signal to a digital bitstream "DEMOD", while the modulator modulates the response "MOD" to the carrier signal. The clock recovery module extracts the RFID carrier frequency and scales it down to a lower frequency signal "Clock" for system operation. The digital logic executes the received RFID command and modulates the response back onto the carrier wave. The digital block comprises a protocol engine and memory.

Fig. 1.10 Conventional RFID architecture utilizes three main blocks: a PMU, a frontend and a digital logic.

Battery-less sensing using RFID technology is an attractive choice for many applications requiring wireless temperature acquisition. The design challenges posed by such systems are to achieve low power, low cost, and high sensor accuracy. Many of the latest commercial/research solutions utilize the combination of RFID frontends, low-power micro-controller units (MCU) and stand-alone sensors [80, 58, 54, 50, 19]. The trade-off of such systems are the high cost, the relatively complex overall system and the relatively high power consumption.

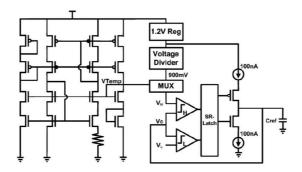

In [80], the commercial RFID sensor chip (Fig. 1.11) integrates no on-chip temperature sensor but an on-chip  $\Sigma\Delta$  ADC. The temperature sensing is accomplished with an off-chip thermistor. With several off-chip discrete components, it is difficult to miniaturize the final product size.

In contrast, state-of-the-art wireless sensor tags implement the sensor directly in the chip without using an MCU [90, 36, 43, 44, 25, 10]. This lets the sensor work in closer conjunction with the RFID functionality and allows for system performance optimization. In addition, system size and complexity can be significantly reduced to enable miniaturized low-cost applications. A

Fig. 1.11 Commercial RFID sensor tag utilizes MCU and many discrete components [80].

wireless glucose sensor [25] is implemented on a contact lens for noninvasive continuous health monitoring. A fully-integrated miniaturized wireless neural sensor [10] is realized for brain-machine interface applications.

In [43], the temperature sensor [23] is implemented in a UHF RFID sensor tag. The accuracy is obtained with  $\pm 0.8$  °C while a sensing range is achieved from -20 °C to 30 °C. The entire conversion time takes 40 ms, so the sampling rate is 25 Samples/s.

A wireless temperature sensor [36] operating from approximately 25 °C to 45 °C with an accuracy of 0.4 °C was demonstrated. The simplified block diagram of the temperature sensor is shown in Fig. 1.12. The voltage  $V_{\rm Temp}$  is obtained in a bias core. Then  $V_{\rm Temp}$  is converted into a clock signal in a relaxation oscillator, whose frequency is temperature dependent. The design utilizes no communication protocol, but modulates the clock frequency directly to the carrier frequency. The design complexity is significantly reduced, while the chip is no longer compatible to the commercial readers.

In [44], a RFID temperature sensor, which utilizes bipolar core and  $\Sigma\Delta$  ADC, achieves an accuracy of [-1,0.8] °C from -20 °C to 50 °C.

Fig. 1.12 Block diagram of the temperature sensor in [36].

#### Supply noise introduction

Every sensor utilizes one voltage as power supply. An ideal supply voltage can be regarded as a stable and noise-free DC voltage with unlimited current drive capability. For the stand-alone sensor, this ideal power supply could be approximately given. However, if the sensor is integrated with other components in a system-on-chip (SoC), the supply voltage is affected by all the components together. Therefore, due to the non-ideal supply voltage, the sensor's performance could be degraded.

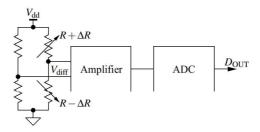

Many state-of-the-art papers discussed the impacts of supply noise in different application scenarios. When designing a Wheatstone bridge [41], a typical resistive sensor consists of four resistors, amplifiers and ADC (Fig. 1.13). The resistors are supplied directly from the supply voltage. If the bridge is balanced, the supply noise will not generate any mismatch at the bridge output. However, the unbalanced bridge will output a significant error under supply mismatch. In addition, the sensor error also shows a non-linearity to the supply voltage mismatch as well, making sensor's inaccuracy compensation even more complicated.

In the phase-locked loop (PLL) design [11], the voltage-controlled oscillator (VCO) is the critical block that defines the phase noise of the output. The VCO

Fig. 1.13 Block diagram of a typical Wheatstone bridge sensor element.

is usually built by inverter-based ring oscillators, which provide the simple and small chip area solutions unlike *LC* tank VCOs. However, this structure suffers a high supply noise sensitivity and high noise floor.

To overcome this problem of supply noise, different papers utilize different strategies. In [11, 15], the PLL introduces a local regulation with dedicated tuning scheme to filter out the supply noise. In [41], the researchers present a force-balanced Wheatstone bridge interface circuit with highly improved overall PSRR and temperature resilience in one circuit. On the other hand, inside a SoC the noise can be reduced directly from the source. The power management units (PMUs) are optimized to provide less-noisy supplies [8, 14, 17].

### 1.4 Task definition and proposal of this thesis

Table 1.1 shows a representative specification of such a sensor unit. In particular, the combination of requirements in terms of dimensions, power consumption and sampling speed poses a high challenge which will be addressed in this thesis. Please notice that the pH sensor is not in the scope of this work.

In this thesis, the design methodology and implementation of fully passive RFID temperature sensor SoC are proposed. To overcome the issues of low accuracy and small operational range for RFID temperature sensors, new ideas have been made in this dissertation.

| Parameter                                    | Target value                                         | Vision                                               |

|----------------------------------------------|------------------------------------------------------|------------------------------------------------------|

| Physical,<br>electrochemical<br>measurements | Temperature, pH value                                | Temperature, pH value<br>Pressure,                   |

| Accuracy of temperature measurements         | ±0.25 °C (10 °C to 40 °C)<br>±0.5 °C (0 °C to 70 °C) | ±0.1 °C (10 °C to 40 °C)<br>±0.25 °C (0 °C to 70 °C) |

| Accuracy of pH measurements                  | ±0.1 pH (10 °C to 40 °C)                             | ±0.05 pH (10 °C to 40 °C)                            |

| Power consumption of the sensor              | <100 μW                                              | <10 µW                                               |

| Supply voltage of the sensor                 | <3 V                                                 | <1 V                                                 |

| Sampling rate                                | >10 Samples/s                                        | >100 Samples/s                                       |

| Chip area                                    | <2 mm <sup>2</sup>                                   | <1 mm <sup>2</sup>                                   |

Table 1.1 Representative specification of a wireless micro-sensor [62]

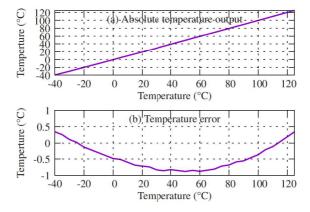

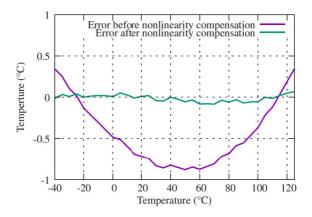

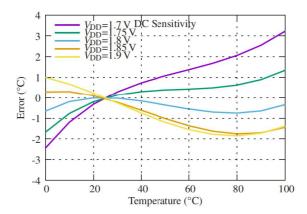

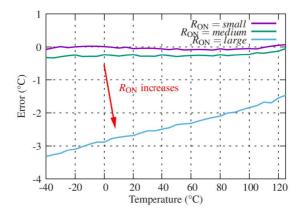

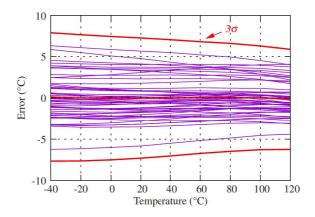

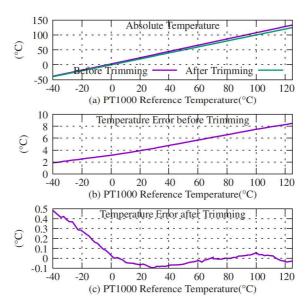

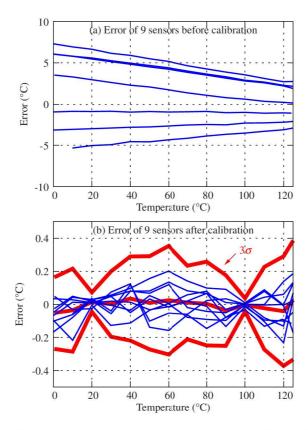

First of all, a novel *time-domain temperature sensor topology* [87, 85] is developed in order to achieve high-accuracy and low-power at same time. The experimental results shows that this temperature sensor achieves [-0.1,0.5] °C from -40 °C to 125 °C, which is the best-in-class performance among the low-power time-domain temperature sensors.

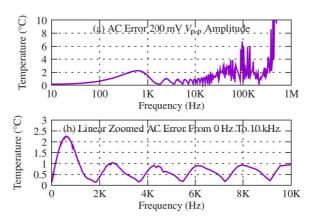

Besides that, since the supply interference is the largest difference between stand-alone and RFID temperature sensors, a complete *methodology* [86, 89, 88, 92, 91] is developed to analyze the generation, the amplification and the digitization of the supply interference. This design methodology is considered as the most significant scientific contribution of this dissertation.

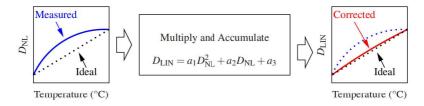

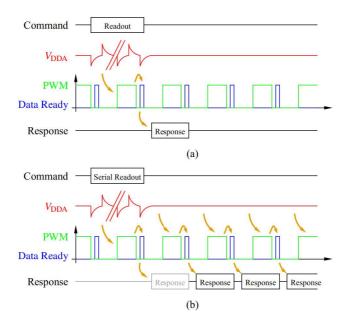

The analysis results show that this new topology provides the least DC interference sensitivity among the current time-domain temperature sensor topologies, while it still suffers from high AC interference sensitivity. To solve this issue a *system level optimization* [90, 89] is achieved by adding a new RFID

command, which can bypass the noisy sensor data but output only the less-noisy ones.

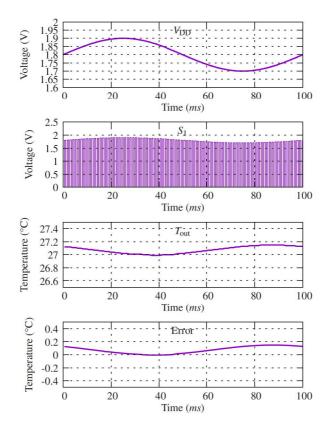

The experimental results [90] show that this proposed RFID temperature sensor achieves  $\pm 0.4\,^{\circ}\text{C}$  (3 $\sigma$ ) from 0 $^{\circ}\text{C}$  to 125 $^{\circ}\text{C}$ , which is the highest accuracy with the widest operational range in comparison with currently reported state-of-the-art RFID temperature sensors. The sampling rate is achieved with 676 Samples/s. The new RFID command improves the noise performance of this RFID temperature sensor by a factor of 16.

#### 1.5 Structure of this thesis

This thesis is organized as follows:

**Chapter 2, Design methodology of supply noise analysis.** The behaviour of the supply noise is analysed in this chapter. The chapter begins with the generation of the supply noise. Then the supply noise is passed through the power management unit and reaches the sensor, affecting the sensor performance. To systematically analyze the supply noise, this chapter utilizes the methodology of modeling, transfer function calculation, verification and comparison.

**Chapter 3, Mixed-signal circuit implementation.** The circuit implementation also introduces many challenges, due to the process, voltage and temperature (PVT) variations. This chapter presents the detailed implementation of the low-power time-domain temperature sensor and the RFID. The temperature sensor is built on an individual test chip, whose experimental results are also presented in this chapter.

**Chapter 4, System integration and physical design.** Because of the supply interference, the system level optimization on the RFID communication is achieved by introducing a new RFID command. Finally, the top-level schematic

and the layout are shown.

**Chapter 5, Experimental results.** This chapter shows the characterization results of this proposed RFID temperature sensor and compares it with the state-of-the-art works.

**Chapter 6, Summary and outlook.** This concluding chapter discusses how the insights developed in this thesis can be put into future RFID sensor designs.

# **Chapter 2**

# Design methodology of supply noise analysis

#### 2.1 Introduction

In order to achieve a low-power high-precision temperature sensing in a RFID SoC, a lot of design concepts can be used. With V-diagram approach, the designer can systematically research the crucial design challenges. And the design space is narrowed down, so that the design goals can be achieved more efficiently. The new chip architecture can be established, if the design constrains can be satisfied.

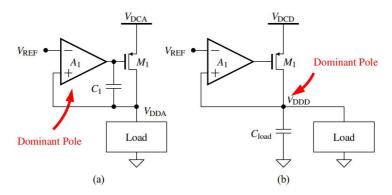

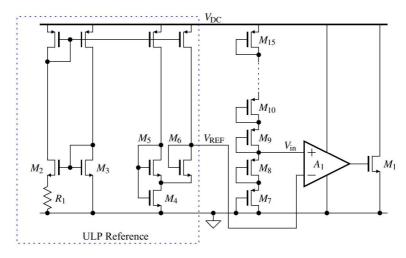

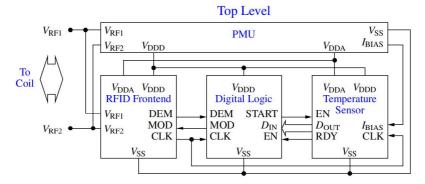

The basic RFID block diagram is already shown in Fig. 1.10. Since RFID needs to cooperate with sensors, the topology needs to be improved. In Fig. 2.1, an additional supply path is added so that the analog blocks are supplied by  $V_{\rm DDA}$ , which is different from the digital blocks. The advantage of this configuration is that the supply noise, which is generated by digital circuits, is not be transmitted directly to the analog circuit. The communication with the sensor

Fig. 2.1 This improved PMU consists of two supply paths and a sensor interface.

is realized by placing the sensor interface in the memory. Thus, the sensor can be controlled and readout by simple RFID write and read commands.

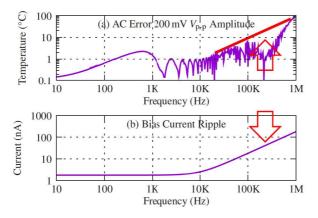

Many RFID sensors suffer low accuracy and small sensing range [36, 43, 44], since the sensors are not only affected by their own noise. The noise from the supply path had a much greater impact on the sensor performance.

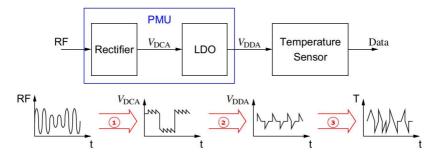

In Fig. 2.2, the design space is narrowed down to three challenges.

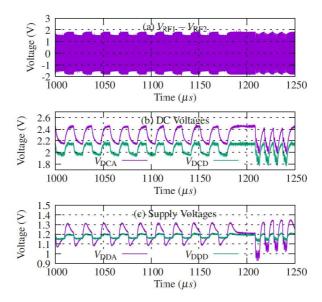

The first challenge is the noise generation, which is related to the RFID functionality. Since the RFID communication is modulated on the RF field, the amplitude changing of the RF field strength can be seen as a dynamic noise. This noise is rectified and added to the unregulated DC voltage  $V_{\rm DCA}$  (Fig. 2.2 ①) in PMU. The second challenge is the noise amplification within PMU (Fig. 2.2 ②). The PMU converts the DC unregulated voltage  $V_{\rm DCA}$  into a DC regulated voltage  $V_{\rm DDA}$ . The supply noise on the regulated supply voltage in state-of-the-art RFID designs exists widely. In [53], it can be seen that approximately 100 mV ripple is generated on a 0.5 V supply during communication. In [90], a 540 mV peak-to-peak AC ripple is measured on a 1.2 V analog supply. The final challenge is the noise digitization from the analog supply voltage to the digital output via the temperature sensor (Fig. 2.2 ③). This results in low sensor accuracy

2.1 Introduction 19

and small sensing range. This effect is observed in [7], but was barely discussed in the paper. Therefore, the analysis of the effects of the supply on the temperature sensors is essential.

Fig. 2.2 The design space is narrowed down into three challenges, which include ①: noise generation, ②: noise amplification and ③: noise digitization.

In Fig. 2.2 ②, the noise amplification can be described by power supply rejection (PSR), which is the supply-to-output characteristic in the frequency domain. Many state-of-the-art designs [8, 14, 17, 48, 45] utilize PSR analysis and optimization of their proposed structures. The analysis of transfer functions went so deep that the parasitic effects are present in their equations. However, their design methodologies, which explain their design trade-offs, are normally not presented and compared. Another problem is that their designs could be dependent on CMOS technology and under certain trade-offs, e.g. input/output range, power consumption, speed or design complexity. As a result, their design techniques could not easily be implemented for daily designs.

In this chapter, the three challenges, namely noise generation, noise amplification and noise digitization, are analyzed and discussed. The noise generation is described and analyzed from different sources in the frequency domain. The noise amplification is investigated by modeling of a typical PMU block. A common approach is presented to analyze and optimize the system behaviour for the crucial component of PMU, namely low-dropout regulator (LDO). The comparison of PSR between transistor design and modeling is demonstrated.

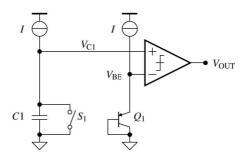

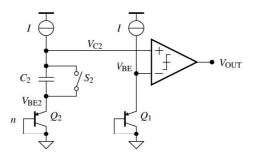

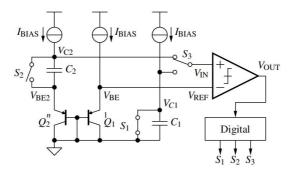

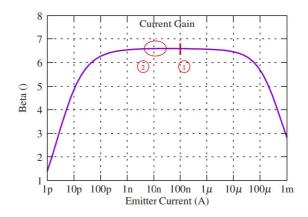

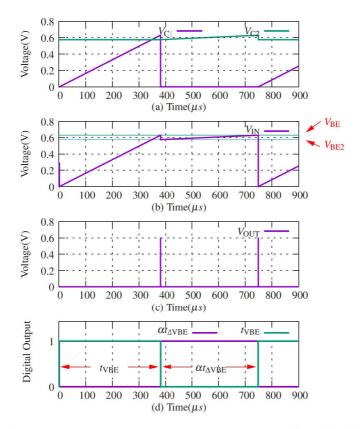

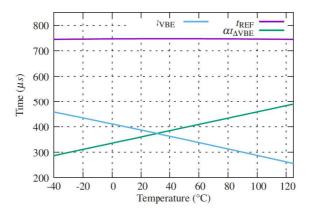

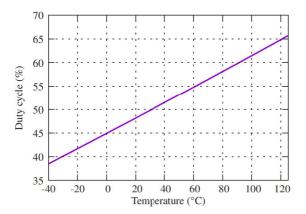

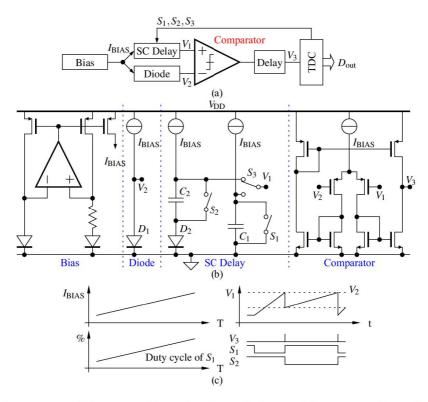

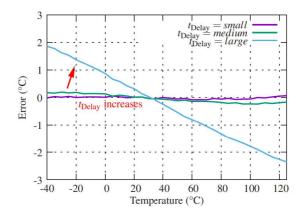

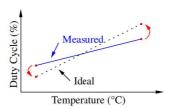

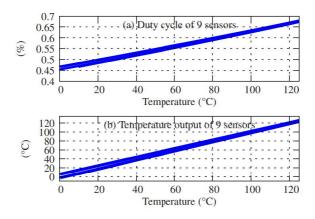

With the modeling, the system behaviour can be explained. The investigation of noise digitization requires a model of the temperature sensor. In this thesis, a novel time-domain low-voltage low-power CMOS on-chip temperature sensor topology for a temperature range from  $-40\,^{\circ}\text{C}$  to  $125\,^{\circ}\text{C}$  is presented. The sensor topology is based on a delay circuit that generates a PWM signal from diode-connected BJTs. The duty cycle of the delay signal is proportional to the absolute temperature. In order to evaluate the noise digitization of different temperature sensors, models of various state-of-the-art temperature sensors are built. All models are built in the same technology, so that the models represent the realistic CMOS circuit. The comparison of the noise sensitivity of the sensor models uncovers the most robust sensor topology, which suffers least from supply noise.

This chapter is organized as follows. In section II, the supply noise generation in the typical RFID architecture is presented. The noise amplification is modeled, simulated and discussed in section III. Section IV describes the concept of the time-domain temperature sensor. The modeling and comparison of noise digitization are explained in section V. Finally, conclusions are drawn in section VI.

#### 2.2 Generation of the supply noise

The ripple can be generated from three different sources [91].

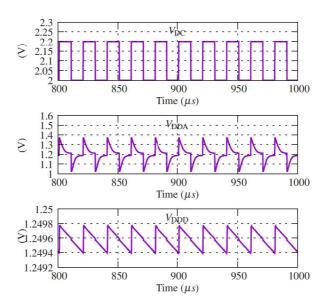

#### Ripple from RF carrier

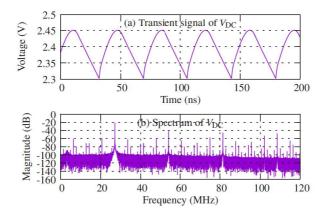

Firstly, the RF carrier brings a significant ripple to  $V_{\rm DCA}$  and  $V_{\rm DCD}$  even after the AC signal is rectified in Fig. 2.1. In Fig. 2.3 (a) a typical  $V_{\rm DC}$  is shown that the ripple oscillates between 2.3 V and 2.45 V. This is because the smoothing capacitors on the output of the rectifier (Fig. 2.1) are normally not large enough, since the smoothing capacitors are built on the chip. In the frequency domain the spectrum of  $V_{\rm DC}$  (Fig. 2.3 (b)) shows that the signal is concentrated

on 27.12 MHz and its harmonics. 27.12 MHz is twice as high as the RF carrier frequency (13.56 MHz), because the modern rectifiers are full wave rectifiers that charge the load twice in a cycle.

Fig. 2.3 (a) The transient signal of a typical  $V_{\rm DC}$  and (b) its spectrum.

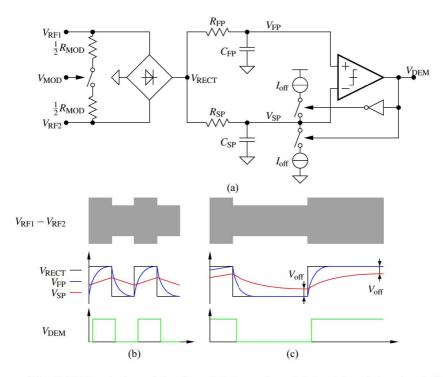

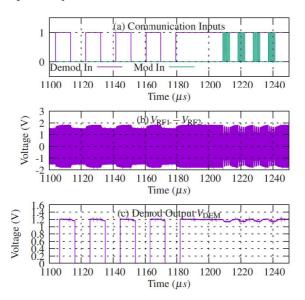

#### Ripple from RFID communication

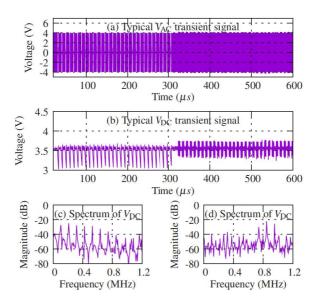

Besides that, the communication between reader and tag is realized by digital modulation Amplitude Shift Keying (ASK), which modulates the amplitude on the RF carrier. The modulation depth of  $V_{\rm AC}$  is typically defined with 0 % and 80 % for IEC/ISO 14443 Type A and Type B [73], respectively. In Fig. 2.4 (a), the reader-to-tag communication (left side) and tag-to-reader communication (right side) utilize 106 kHz and 848 kHz, respectively. Due to the amplitude modulation, the rectifier output  $V_{\rm DC}$  in Fig. 2.4 (b) generates significant voltage drops, since the load constantly draws current from the smoothing cap. The voltage drops are dependent on the load, the smoothing cap and the rectifier output resistance. In Fig. 2.4 (c), the spikes happen exactly at 106 kHz and its harmonics. Since the tag responses (106 kHz) are modulated on a 848 kHz subcarrier frequency according to the protocol, the spectrum of the response signal

Fig. 2.4 (a) A typical RF transmission waveform  $V_{\rm AC}$  with reader-to-tag communication (left) and tag-to-reader communication (right) and (b) the corresponding rectified voltage  $V_{\rm DC}$  with the spectrum of  $V_{\rm DC}$  for (c) reader-to-tag communication and (d) tag-to-reader communication

in Fig. 2.4 (d) clearly shows three spikes at 742 kHz, 848 kHz and 954 kHz. In General, the communication ripples are approximately distributed between 100 kHz and 1 MHz.

#### Ripple from incoming power and the load

At the end, the DC level of  $V_{\rm DCA}$  and  $V_{\rm DCD}$  is determined by the incoming power and load, namely reader output power, geometry and system power consumption. The induced voltage changing is basically in the low-frequency band, due to the fact that geometry and load condition change relatively slowly.

Fig. 2.5 Using V-diagram to systematically analyze the amplification of the supply noise

#### 2.3 Amplification of the supply noise

From the block diagram in Fig. 2.1, the interference can pass to the analog supply voltage  $V_{\rm DDA}$  on two paths. Firstly, the interference on  $V_{\rm DCA}$  is directly applied to the LDO. The second path comes from the bandgap voltage reference, which provides the reference voltage for the LDO.

Among the three independent processes, the amplification of the supply noise is the most important, but is also difficult to analyse. The challenge is: How can the critical design aspects for the system behaviour problem be found efficiently and rapidly? In this case, the problem is to analyse the conducted ripple from the rectifier output to the sensor input. Based on the V-diagram introduced in Chapter 1, the entire process can be divided into three sub-processes.

Firstly, the problem must be identified. Since this problem has already been shown in various works, it should not be difficult to recreate the failure scenario. The power signal  $V_{\rm DCA}$  in Fig. 2.2 is passed directly to the LDO. The LDO should be analyzed in any case. However, another hidden path can also affect

the LDO output. In Fig. 2.1, the bandgap reference takes  $V_{\rm DCA}$  as supply voltage and outputs the reference voltage used by the LDO. Therefore, the bandgap and the LDO must be analyzed together.

The second step is to implement the modeling, which simplifies the analysis of the circuit. The transistor-level circuit contains too much information, which is sometimes difficult to separate the critical parameters and the non-critical ones. The modeling captures the essential properties of a transistor-level circuit, so that the critical parameters can be extracted directly from these essential properties. The way the modeling is built can be decided by the designer.

The final step is to verify the modeling by comparing the simulation results of the modeling to the simulation results of the transistor circuit. The modeling of the sub-blocks must first be verified, until the simulation results of the transistor circuit and the modeling are matched. The system modeling is then built from the sub-block models. The modeling should be trimmed until the modeling reveals the problem exactly.

With modeling, the critical parameters that dominate the problem can analyzed much more easily. Thus, the key for solving the problem can be easily found and new ideas for improvement can be developed.

#### 2.3.1 Problem identification

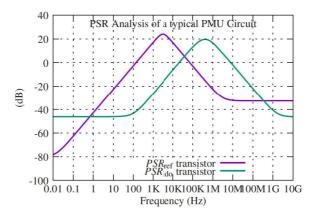

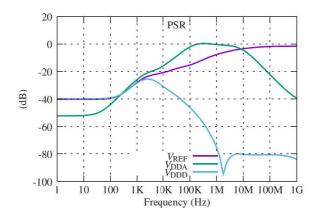

The PSR is defined as the gain from the input supply signal to the output supply signal in the frequency domain. A typical low power PMU design is utilized to simulate for modeling. The results of the PSR simulation of a bandgap reference and an LDO are shown in Fig. 2.6.

The DC PSR curves of both the bandgap reference and the LDO are below zero with the number of -77 dB and -46 dB, respectively. This means that the DC supply noise is significantly reduced. However, if the frequency goes higher, the PSR gets worse. From 130 Hz to 75 kHz, the PSR of the bandgap reference is above 0 dB. In this frequency range, the supply noise is amplified. For LDO, the frequency range for noise amplification is between 20 kHz to 8 MHz. Un-

Fig. 2.6 The PSR simulations of a bandgap and an LDO in the frequency domain.

fortunately, these frequency ranges are widely used by sensor operations and RFID communication. From the simulation of PSR, the problem is identified that the PMU amplifies the supply noise in a wide frequency range.

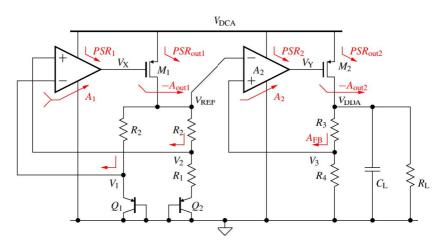

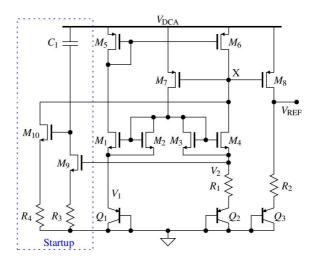

# 2.3.2 Modeling implementation

The typical combination of bandgap and LDO for power analysis is shown in Fig. 2.7. On the left, the bandgap voltage reference consists of a bandgap core  $(Q_1, Q_2, R_1 \text{ and } R_2)$ , an error amplifier and a transistor  $M_1$ . With the feedback loop, the bandgap core is properly biased and generates the reference voltage  $V_{\text{REF}}$ . On the right, the voltage  $V_{\text{REF}}$  is passed to the LDO, which is formed by  $A_2$ ,  $M_2$ ,  $R_3$  and  $R_4$ . The output regulated supply voltage  $V_{\text{DDA}}$  is generated by the LDO and supplies the load described by  $R_{\text{L}}$  and  $C_{\text{L}}$ .

In Fig. 2.8, the blocks are summarized to analyze the signal flows and the transfer function. Every block represents a single gain stage with voltage input and voltage output. Each "macro circuit" is built by the signal gain stage, e.g.  $A_2$ , and supply gain stage, e.g.  $PSR_2$ , as long as the gain stage consumes power

Fig. 2.7 The simplified circuit [91] combines the voltage reference and LDO for transfer function analysis.

Fig. 2.8 To analyze the transfer function from  $\Delta V_{DCA}$  to  $\Delta V_{DDA}$ , the signal flow graph of the circuit [91] is drawn with the consideration of  $\Delta V_{DCA}$ .

from supply. The signals of two gain stages are summed to generate the output signal, since the real circuit has only one output port. All blocks without  $A_{\rm FB}$  are modeled with one pole to reveal the system behaviour without complicating the calculation. Please notice that the bandgap error amplifier and feedback are combined to a common gain stage to simplify the calculation. Table 2.1 summarizes the models for the further analysis.

| Macro circuit                     | Signal gain stage                                                                 | Supply gain stage                                                                     |

|-----------------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| Voltage reference error amplifier | $A_1 = \frac{A_{1,DC}}{1 + \frac{s}{\omega_1}}$                                   | $PSR_1 = \frac{PSR_{1,DC}}{1 + \frac{s}{\omega_1}}$                                   |

| Voltage reference output stage    | $A_{\text{out1}} = \frac{A_{\text{out1,DC}}}{1 + \frac{s}{\omega_{\text{out1}}}}$ | $PSR_{\text{out1}} = \frac{PSR_{\text{out1,DC}}}{1 + \frac{s}{\omega_{\text{out1}}}}$ |

| LDO<br>Error amplifier            | $A_2 = \frac{A_{2,DC}}{1 + \frac{s}{\omega_2}}$                                   | $PSR_2 = \frac{PSR_{2,DC}}{1 + \frac{s}{\omega_2}}$                                   |

| LDO<br>Output stage               | $A_{	ext{out2}} = rac{A_{	ext{out2,DC}}}{1 + rac{s}{\omega_{	ext{out2}}}}$      | $PSR_{out2} = \frac{PSR_{out2,DC}}{1 + \frac{s}{\omega_{out2}}}$                      |

Table 2.1 Summarized parameters for the further analysis

# 2.3.3 Transfer function calculation

In Fig. 2.8, the system behaviours can be written as:

$$\Delta V_{\rm X} = \Delta V_{\rm REF} A_1 + \Delta V_{\rm DCA} PSR_1, \tag{2.1}$$

$$\Delta V_{\text{REF}} = -\Delta V_{\text{X}} A_{\text{out1}} + \Delta V_{\text{DCA}} P S R_{\text{out1}}, \qquad (2.2)$$

$$\Delta V_{\rm Y} = (\Delta V_{\rm DDA} A_{\rm FB} - \Delta V_{\rm REF}) A_2 + \Delta V_{\rm DCA} PSR_2, \tag{2.3}$$

$$\Delta V_{\rm DDA} = -\Delta V_{\rm Y} A_{\rm out2} + \Delta V_{\rm DCA} P S R_{\rm out2}. \tag{2.4}$$

The equations from (2.1) to (2.4) can be simplified as:

$$\Delta V_{\text{DDA}} = \frac{PSR_{\text{out2}} - A_{\text{out2}}PSR_2}{1 + A_2A_{\text{FB}}A_{\text{out2}}} \Delta V_{\text{DCA}} + \frac{A_2A_{\text{out2}}}{1 + A_2A_{\text{FB}}A_{\text{out2}}} \Delta V_{\text{REF}}, \qquad (2.5)$$

$$\Delta V_{\text{REF}} = \frac{PSR_{\text{out1}} - A_{\text{out1}}PSR_1}{1 + A_1A_{\text{out1}}} \Delta V_{\text{DCA}}. \qquad (2.6)$$

$$\Delta V_{\text{REF}} = \frac{PSR_{\text{out1}} - A_{\text{out1}}PSR_1}{1 + A_1A_{\text{out1}}} \Delta V_{\text{DCA}}.$$

(2.6)

The PSR from input supply changing  $\Delta V_{\rm DCA}$  to output signal changing  $\Delta V_{\rm DDA}$  can be expressed as:

$$PSR = \frac{\Delta V_{\rm DDA}}{\Delta V_{\rm DCA}},\tag{2.7}$$

$$= PSR_{\rm ldo} + A_{\rm cl.ldo} \cdot PSR_{\rm ref}, \tag{2.8}$$

$$= \frac{PSR_{\text{out2}} - A_{\text{out2}}PSR_2}{1 + A_2A_{\text{FB}}A_{\text{out2}}} + \frac{A_2A_{\text{out2}}}{1 + A_2A_{\text{FB}}A_{\text{out2}}} \cdot \frac{PSR_{\text{out1}} - A_{\text{out1}}PSR_1}{1 + A_1A_{\text{out1}}}. \quad (2.9)$$

The equation (2.9) has three terms. The term 1 PSR<sub>ldo</sub> is PSR of LDO, which is only dependent on the LDO itself. The second term  $A_{cl,ldo}$  indicates the closed-loop gain of the LDO, which is approximately  $1/A_{\rm FB}$  at DC. he term 3 PSR<sub>ref</sub> is contributed by the PSR of the bandgap. The product of term 2 and term 3 means that the PSR of the bandgap voltage reference is amplified by the LDO.

#### PSR of the LDO PSR<sub>Ido</sub>

In Fig. 2.7,  $A_{\text{out2}}$  can be seen as common-source stage, while  $PSR_{\text{out2}}$  can be understood as common-gate stage. The DC gain of  $A_{out2}$  and  $PSR_{out2}$  can be expressed by:

$$A_{\text{out2,DC}} = g_{\text{m2}} r_{\text{out}}, \tag{2.10}$$

$$PSR_{\text{out2,DC}} = (g_{\text{m2}} + g_{\text{ds2}})r_{\text{out}},$$

(2.11)

where  $g_{\rm m2}$  and  $g_{\rm ds2}$  are the small-signal transconductance of gate-source voltage and drain-source voltage,  $r_{\rm out}$  is the output resistance. Since  $g_{\rm ds2} \ll g_{\rm m2}$ ,  $A_{\rm out2,DC}$  is approximately same as  $PSR_{\rm out2,DC}$ .

Combing the equations of Table 2.1,  $PSR_{ldo}$  of the equation (2.9) can be written as [92]:

$$PSR_{\text{ldo}} = \frac{\left(-A_{\text{out2,DC}}PSR_{2,\text{DC}}\omega_2 - PSR_{\text{out2,DC}}(s+\omega_2)\right)\omega_{\text{out2}}}{(s+\omega_2)(s+\omega_{\text{out2}}) + A_{2,\text{DC}}A_{\text{FB}}A_{\text{out2,DC}}\omega_2\omega_{\text{out2}}},$$

(2.12)

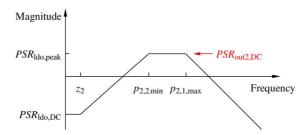

$$= PSR_{\rm Ido,DC} \frac{1 + \frac{s}{z_2}}{(1 + \frac{s}{p_{2,1}})(1 + \frac{s}{p_{2,2}})}.$$

(2.13)

The equation (2.13) shows two poles and one zero, so that the position of zero and poles needs to be analyzed in order to reveal the system behaviour.

The DC gain of  $PSR_{1do}$  can be expressed by:

$$PSR_{\rm ldo,DC} \approx \left| \frac{PSR_{\rm out2,DC}}{A_{\rm out2,DC}} - PSR_{\rm 2,DC} \right| \frac{1}{A_{\rm 2,DC}A_{\rm FB}},$$

(2.14)

$$\approx |1 - PSR_{2,DC}| \frac{1}{A_{2,DC}A_{FB}}.$$

$$\downarrow \qquad \qquad \downarrow \qquad \qquad \qquad \downarrow \qquad \qquad \qquad \downarrow \qquad \qquad$$

Two terms are presented in equation (2.15). The term 2 defines the fundamental value, which comes from the error amplifier and feed back. More DC gain of the error amplifier generates enhanced DC PSR (more DC noise reduction). The term 1, which is dependent on  $PSR_{2,DC}$ , is a factor that amplifies the fundamental value. By making  $PSR_{2,DC}$  as close as 1 ( $PSR_{out2,DC}/A_{out2,DC}$ ), the DC PSR can be significantly reduced.

The zero of equation (2.13) can be written as:

$$z_2 \approx \left| 1 - \frac{A_{\text{out2,DC}} PSR_{2,\text{DC}}}{PSR_{\text{out2,DC}}} \right| \omega_2,$$

(2.16)

$$\approx |1 - PSR_{2,DC}|\omega_2. \tag{2.17}$$

The term 2 of equation (2.17) is linked to the 3 dB frequency of the error amplifier ( $\omega_2$ ). More bandwidth of the error amplifier results in higher frequency of the zero. The term 2 is again amplified by a factor (term 1), which is similar as term 1 in equation (2.15).

By calculating  $z_2/PSR_{\rm ldo,DC}$ , a bandwidth (BW) can be obtained:

$$BW = \frac{z_2}{PSR_{\rm ldo,DC}} \approx \frac{A_{\rm out2,DC}A_{\rm 2,DC}A_{\rm FB}}{PSR_{\rm out2,DC}}\omega_2, \tag{2.18}$$

$$\approx A_{2,DC}A_{FB}\omega_2.$$

(2.19)

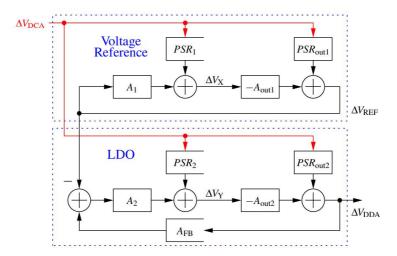

It can be seen that the zero and DC PSR are dependent on  $PSR_{2,DC}$ , while their ratio is independent of it. In the Bode diagram (Fig. 2.9), the movement of zero starts with  $PSR_{2,DC} = 0$  (①). As  $PSR_{2,DC}$  increases and moves toward 1, the DC PSR reduces, while the zero moves to the lower frequency (②). If  $PSR_{2,DC}$  is larger than 1 and continues to rise, the corner turns back, so that DC PSR increases and zero moves to a higher frequency (③). When  $PSR_{2,DC}$  is near  $A_{2,DC}A_{FB}$  (④), the DC PSR becomes 0 dB, while the zero becomes BW ( $A_{2,DC}A_{FB}\omega_2$ ).

Fig. 2.9 The zero and DC PSR move as  $PSR_{2,DC}$  increases from 0 to  $A_{2,DC}A_{FB}$ .

The two poles of LDO PSR can be calculated as:

$$p_{2,1} = \frac{1}{2} \left( \omega_2 + \omega_{\text{out2}} + \sqrt{(\omega_2 - \omega_{\text{out2}})^2 - 4A_{\text{ol2,DC}}\omega_2\omega_{\text{out2}}} \right),$$

(2.20)

$$p_{2,1} = \frac{1}{2} \left( \omega_2 + \omega_{\text{out2}} + \sqrt{(\omega_2 - \omega_{\text{out2}})^2 - 4A_{\text{ol2,DC}} \omega_2 \omega_{\text{out2}}} \right),$$

$$p_{2,2} = \frac{1}{2} \left( \omega_2 + \omega_{\text{out2}} - \sqrt{(\omega_2 - \omega_{\text{out2}})^2 - 4A_{\text{ol2,DC}} \omega_2 \omega_{\text{out2}}} \right).$$

(2.20)

If  $(\omega_2 - \omega_{\text{out2}})^2 - 4A_{\text{ol2,DC}}\omega_2\omega_{\text{out2}} > 0$ , the resulted poles are real. Otherwise the poles are complex conjugate pairs, which will generate a magnitude spike on the frequency response in the bode plot.

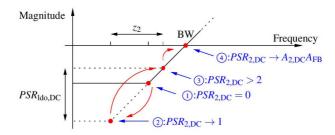

If the poles are real, they are mirrored by the central point of  $\frac{1}{2}(\omega_2 + \omega_{\text{out}2})$ . Their distance to the central point is defined by the ratio  $R = \frac{\omega_{\text{out2}}}{\omega_2}$ . The more the ratio is, the more distance they have. The poles in Fig. 2.10 are limited by:

$$p_{2,2,\min} = \lim_{R \to \infty} p_{2,2} \approx A_{\text{ol2,DC}} \omega_2, \tag{2.22}$$

$$p_{2,1,\text{max}} = \lim_{R \to \infty} p_{2,1} \approx \omega_{\text{out2}}.$$

(2.23)

Fig. 2.10 The real poles are mirrored by  $\frac{1}{2}(\omega_2 + \omega_{\text{out}2})$

The theoretical peak PSR can be obtained in two cases.

If the zero is the smallest among the zero and poles. The magnitude of the frequency response increases after the zero and reaches the maximum between two poles. The theoretical peak PSR (Fig. 2.11) occurs only when the two poles are far away from each other, i.e.,  $p_{2,1} \ll p_{2,2}$ . In this case the peak PSR can be calculated by:

$$PSR_{\rm Ido,peak} = PSR_{\rm Ido,DC} \frac{1 + \frac{f_{\rm Ido,peak}}{z_2}}{(1 + \frac{f_{\rm Ido,peak}}{P_{2,1,\rm max}})(1 + \frac{f_{\rm Ido,peak}}{P_{2,2,\rm min}})},$$

$$\approx PSR_{\rm Ido,DC} \frac{\frac{f_{\rm Ido,peak}}{z_2}}{1 \cdot \frac{f_{\rm Ido,peak}}{P_{2,2,\rm min}}},$$

$$\approx PSR_{\rm Ido,DC} \frac{p_{2,2,\rm min}}{z_2},$$

$$(2.24)$$

$$\approx PSR_{\rm ldo,DC} \frac{\frac{f_{\rm ldo,peak}}{z_2}}{1 \cdot \frac{f_{\rm ldo,peak}}{p_2 \cdot 2 \min}},$$

(2.25)

$$\approx PSR_{\rm ldo,DC} \frac{p_{2,2,\rm min}}{z_2},\tag{2.26}$$

$$= \frac{\left| \frac{PSR_{\text{out2,DC}}}{A_{\text{out2,DC}}} - PSR_{2,\text{DC}} \right|}{A_{2,\text{DC}}A_{\text{FB}}} \frac{A_{\text{ol2,DC}}\omega_2}{\left| 1 - \frac{A_{\text{out2,DC}}PSR_{2,\text{DC}}}{PSR_{\text{out2,DC}}} \right|} \omega_2, \tag{2.27}$$

$$= \frac{\left(-PSR_{2,DC} + \frac{PSR_{\text{out2,DC}}}{A_{\text{out2,DC}}}\right)}{A_{2,DC}A_{FB}} \cdot \frac{A_{2,DC}A_{FB}A_{\text{out2,DC}}\omega_2}{\left(1 - \frac{A_{\text{out2,DC}}PSR_{2,DC}}{PSR_{\text{out2,DC}}}\right)\omega_2}, \quad (2.28)$$

$$= PSR_{\text{out2,DC}}. (2.29)$$

Fig. 2.11 The theoretical peak PSR is obtained when the two poles are far away from each other, so that a flat region is created between the poles.

If one pole is the smallest among the zero and poles. In this case the DC PSR is the peak PSR, since the magnitude doesn't increase any more.

$$PSR_{\text{ldo,peak}} = PSR_{\text{ldo,DC}} = \left| \frac{PSR_{\text{out2,DC}}}{A_{\text{out2,DC}}} - PSR_{2,\text{DC}} \right| \frac{1}{A_{2,\text{DC}}A_{\text{FB}}}.$$

(2.30)

## Closed-loop gain of the LDO $A_{cl.ldo}$

The closed-loop gain of the LDO is expressed by:

$$A_{\text{cl,ldo}} = \frac{A_2 A_{\text{out2}}}{1 + A_2 A_{\text{FB}} A_{\text{out2}}},\tag{2.31}$$

$$= \frac{A_{2,\text{DC}}A_{\text{out2},\text{DC}}\omega_2\omega_{\text{out2}}}{(s+\omega_2)(s+\omega_{\text{out2}}) + A_{2,\text{DC}}A_{\text{FB}}A_{\text{out2},\text{DC}}\omega_2\omega_{\text{out2}}}.$$

(2.32)

Assuming  $A_{2,DC}A_{out2,DC} \gg 1$ , the DC closed-loop gain is approximately  $1/A_{FB}$ . The closed-loop gain has two poles:

$$p_{2,1} = \frac{1}{2} \left( \omega_2 + \omega_{\text{out}2} + \sqrt{(\omega_2 - \omega_{\text{out}2})^2 - 4A_{\text{ol2,DC}}\omega_2\omega_{\text{out}2}} \right),$$

(2.33)

$$p_{2,2} = \frac{1}{2} \left( \omega_2 + \omega_{\text{out2}} - \sqrt{(\omega_2 - \omega_{\text{out2}})^2 - 4A_{\text{ol2,DC}}\omega_2\omega_{\text{out2}}} \right).$$

(2.34)

It can be seen that the poles are the same as equations (2.20) and (2.21).

# **PSR** of the voltage reference *PSR*<sub>ref</sub>

In Fig. 2.8 it can be noticed that the voltage reference shares a similarity with LDO in the block structure. The calculation of the bandgap reference can be

directly given as:

$$PSR_{\text{ref}} = \frac{(A_{\text{out1,DC}} PSR_{1,\text{DC}} \omega_1 + PSR_{\text{out1,DC}} (s + \omega_1)) \omega_{\text{out1}}}{(s + \omega_1)(s + \omega_{\text{out1}}) + A_{1,\text{DC}} A_{\text{out1,DC}} \omega_1 \omega_{\text{out1}}},$$

(2.35)

$$= PSR_{\text{ref,DC}} \frac{1 + \frac{s}{z_1}}{(1 + \frac{s}{p_{1,1}})(1 + \frac{s}{p_{1,2}})},$$

(2.36)

$$PSR_{\text{ref,DC}} \approx |1 - PSR_{1,\text{DC}}| \frac{1}{A_{1,\text{DC}}},\tag{2.37}$$

$$z_1 \approx |1 - PSR_{1,DC}| \omega_1, \tag{2.38}$$

$$p_{1,1} = \frac{1}{2} \left( \omega_{l} + \omega_{\text{out}1} + \sqrt{(\omega_{l} - \omega_{\text{out}1})^{2} - 4A_{\text{oll,DC}}\omega_{l}\omega_{\text{out}1}} \right),$$

(2.39)

$$p_{1,2} = \frac{1}{2} \left( \omega_{l} + \omega_{\text{out1}} - \sqrt{(\omega_{l} - \omega_{\text{out1}})^{2} - 4A_{\text{ol1,DC}}\omega_{l}\omega_{\text{out1}}} \right). \quad (2.40)$$

# 2.3.4 Modeling verification

To verify the theory, the model is simulated in comparison to the previous transistor-level low-power PMU design. The parameters listed in Table 2.2 are simply extracted from the sub-blocks of a conventional bandgap and LDO design. The aim is to check whether the PSR simulations are agreed between the transistor top level and the modeling, which utilizes the parameters of the analog sub-blocks. under this circumstance, the value of each parameter is irrelevant.

Verified by "Analog Insydes" [60], the PSR transfer function of model and transistor-level design agree to each other. The PSR characterization can be

| Parameter                                              | Extracted value | Parameter                       | Extracted value  |

|--------------------------------------------------------|-----------------|---------------------------------|------------------|

| $A_{\rm out2,DC}$                                      | 9.33 (19.3 dB)  | $A_{2,DC}$                      | 47.62 (33.6 dB)  |

| $PSR_{out2,DC}$                                        | 9.57 (19.6 dB)  | $PSR_{2,DC}$                    | 0.79 (-2  dB)    |

| $f_{\rm out2} \left(\omega_{\rm out2}/2\pi\right)$     | 887 kHz         | $f_2\left(\omega_2/2\pi\right)$ | 445 Hz           |

| $A_{ m FB}$                                            | 1 (0  dB)       | $A_{ m ol2,DC}$                 | 444.29 (52.9 dB) |

| $A_{ m out1,DC}$                                       | 16.58 (24.4 dB) | $A_{1,\mathrm{DC}}$             | 21.66 (26.7 dB)  |

| $PSR_{\text{out1,DC}}$                                 | 16.62 (24.4 dB) | $PSR_{1,DC}$                    | 1 (0 dB)         |

| $f_{\rm out1} \left( \omega_{\rm out1} / 2\pi \right)$ | 4.47 kHz        | $f_1\left(\omega_1/2\pi\right)$ | 5.88 Hz          |

|                                                        |                 | $A_{ m ol1,DC}$                 | 359.12 (51.1 dB) |

|                                                        |                 |                                 |                  |

Table 2.2 Extracted parameters of a typical low-power PMU design [92]

expressed by:

$$PSR_{\text{Ido,DC}} = 0.00494 = -46 \, \text{dB}, \qquad (2.41)$$

$$z_2 = 102 \, \text{Hz}, \qquad (2.42)$$

$$p_{2,1} = 589068 \, \text{Hz}, \qquad (2.43)$$

$$p_{2,2} = 298377 \, \text{Hz}, \qquad (2.44)$$

$$PSR_{\text{ref,DC}} = 0.000145 = -77 \, \text{dB}, \qquad (2.45)$$

$$z_1 = 14.15 \, \text{mHz}, \qquad (2.46)$$

$$p_{1,1} = 2237 + 1497 \, \text{i} \, \text{Hz}, \qquad (2.47)$$

$$p_{1,2} = 2237 - 1497 \, \text{i} \, \text{Hz}. \qquad (2.48)$$

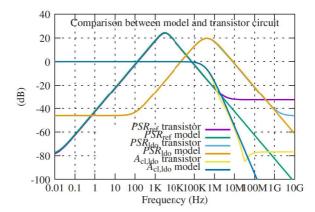

In Fig. 2.12 the simulation results of the circuit and the model are compared. All three key parameters, namely  $PSR_{\text{ldo}}$ ,  $PSR_{\text{ref}}$  and  $A_{\text{cl,ldo}}$ , are simulated from 10 mHz to 10 GHz.

From 10 Hz to 1 GHz, the two curves of  $PSR_{ldo}$  are relative close. From 1 GHz, the PSR of the model drops continuously with the slope of  $-20 \, dB/Decade$ , while the PSR of the circuit becomes flat. The reason of this effect is the parasitic capacitor  $C_{DS}$  of the LDO pass transistor. In Fig. 2.7, with the drain-source capacitor  $C_{DS}$  of  $M_2$  and the capacitor load  $C_L$ , the output voltage  $V_{DDA}$  is a frac-

Fig. 2.12 The simulation results of a transistor-level circuit and its extracted model

tion of the input voltage  $V_{\rm DCA}$ . The effect usually occurs in the high frequency range that is already outside the circuit's operational range.

For  $PSR_{ref}$ , the poles and zeros are lower than those of LDO, since the reference does not drive an active load, only the gate of LDO. From 10 mHz to 1 MHz, the two curves overlap. As predicted from the model and the calculation, the DC PSR reaches -77 dB, while the zero is located at 14.15 mHz. The peak PSR ( $\approx$ 24 dB) is reached at the poles ( $\approx$ 3 kHz), which are complex conjugate poles. Beyond 1 MHz the two curves drift away, due to the parasitic capacitor of the PMOS transistor ( $M_1$  in Fig. 2.7).

Finally, the closed-loop gain  $A_{\rm cl,ldo}$  remains 0 dB until the first pole. Since the two poles are close to each other, the curve bends and drops further with  $-40\,\rm dB$ . In the transistor level simulation, additional poles and zeros are shown from 1 MHz to 10 MHz, but they are insignificant, since the gain is low. If the frequency is above 30 MHz, the closed-loop gain stays flat, while the model continuously decreases. This is because the high-frequency AC signal couples directly from the input to the output. Since this effect happens in the high frequency with low gain, it is not taken into account in the modeling.

Fig. 2.13 The overall power path simulation results [91]

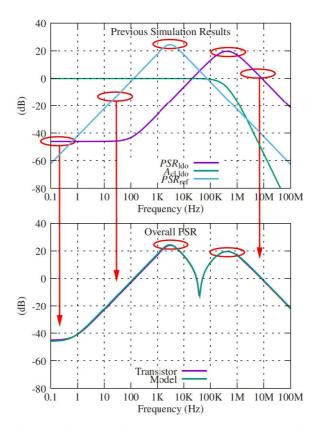

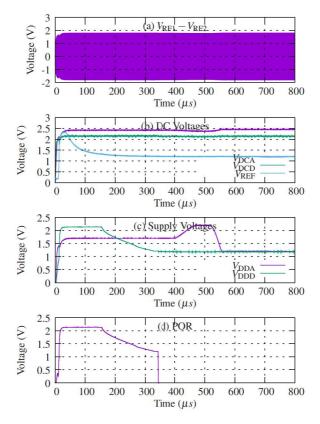

The combination of voltage reference and LDO can reveal the system behaviour. In Fig. 2.13, the overall PSR of the system can be divided into three areas.

• From DC to approximately 1 Hz, the system PSR follows  $PSR_{\text{ldo}}$ , since  $PSR_{\text{ldo}}$  is more significant than  $A_{\text{cl,ldo}} \cdot PSR_{\text{ref}}$ .

- From approximately 1 Hz to 40 kHz, the reference dominants the overall PSR, because the reference operates at a lower frequency than LDO. At approximately 3 kHz PSR<sub>ref</sub> reaches its maximum value, so that the system PSR reaches this value as well.

- Beyond approximately 40 kHz, the PSR<sub>Ido</sub> starts to be significant, while the overall PSR reaches another peak at approximately 400 kHz.

In Fig. 2.13, the peak PSR of the reference and LDO are approximately 24 dB and 20 dB, respectively. The peak PSR of both blocks is located between their two poles. The peak value can be written as:

$$PSR_{\text{Ido,peak}} = PSR_{\text{out2,DC}},$$

(2.49)

$$PSR_{\text{ref,peak}} = PSR_{\text{out1,DC}},$$

(2.50)

where  $PSR_{\text{out2,DC}}$  and  $PSR_{\text{out1,DC}}$  are the DC gain of  $PSR_{\text{out2}}$  and  $PSR_{\text{out1}}$  in Fig. 2.8, respectively. Since they both use PMOS transistor as pass transistor, they share the similar value.

The result shows that both reference and LDO have a significant impact on the overall performance. As long as the peak PSR is a positive value, it is unavoidable that part of the supply noise will be amplified and transferred to the noise-sensitive loads, since multiple frequencies present in such complex systems.

# 2.3.5 Methodology for LDO PSR optimization

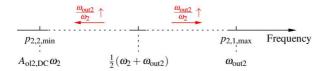

As manipulating the discussed parameters, the methodology for LDO PSR optimization can be obtained. Since two different relationships of  $\omega_2$  and  $\omega_{out2}$  can lead to different design strategies, it is necessary to compare the methodologies to find out the optimized design.

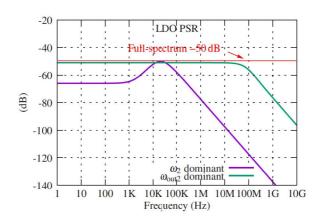

#### Desired PSR with desired bandwidth

Table 2.3 shows two strategies to achieve -50 dB PSR at 100 kHz.

Table 2.3 Design methodology comparison for PSR -50 dB@100 kHz [92]

| Parameter                                                                           | $\omega_2$ dominant                               | $\omega_{	ext{out2}}$ dominant                       |

|-------------------------------------------------------------------------------------|---------------------------------------------------|------------------------------------------------------|

| $A_{2,\mathrm{DC}}$ $PSR_{2,\mathrm{DC}}$ $f_2\left(\omega_2/2\pi\right)$           | 70 dB<br>-6 dB<br>10 kHz                          | 20 dB<br>0.34 dB<br>3.16 MHz                         |

| $A_{ m out2,DC} \ PSR_{ m out2,DC} \ f_{ m out2} \left(\omega_{ m out2}/2\pi ight)$ | 20 dB<br>20.4 dB<br>632 MHz                       | 20 dB<br>20.4 dB<br>15.8 kHz                         |

| PSR <sub>Ido,DC</sub> z <sub>2</sub> P <sub>2,1</sub> P <sub>2,2</sub>              | -75 dB<br>5.2 kHz<br>316+316i MHz<br>316-316i MHz | -60 dB<br>30 kHz<br>1.59+1.59i MHz<br>1.59-1.59i MHz |

| Design constrains                                                                   | Output stage needs high bandwidth.                | Off-chip cap and dedicated $PSR_{2,DC}$ are needed.  |

| Reference                                                                           | N/A                                               | [17, 28, 14]                                         |

The red font shows the absolute critical parameters, while the blue font and the black font represent less critical and relax parameters, respectively.

If  $\omega_2$  is set to dominant pole,  $A_{2,DC}$  and  $f_2$  are determined first, since BW is already defined by the specification.

The BW can be calculated as:

$$BW = \frac{100 \,\text{kHz}}{-50 \,\text{dB}} = \frac{100 \,\text{kHz}}{3.16 \times 10^{-3}} = 31.6 \,\text{MHz}.$$

(2.51)

The DC gain of the error amplifier  $A_{2,DC}$  must be above 50 dB, so that the requirement of  $\omega_2$  is not crucial. Assuming  $A_{FB} = 1$ , from equation (2.19), the

pole of the error amplifier  $f_2$  ( $\omega_2/2\pi$ ) can be determined by:

$$f_2 \ge \frac{BW}{A_{\text{FB}}A_{2,\text{DC}}} = \frac{31.6\,\text{MHz}}{70\,\text{dB}},$$

(2.52)

$$= 10 \,\mathrm{kHz}.$$

(2.53)

Since the load defines the current through the output stage,  $A_{\text{out2,DC}}$  and  $PSR_{\text{out2,DC}}$  are decided with 20 dB and 20.4 dB, respectively. The overall open-loop gain can be calculated as:

$$A_{\text{ol,ldo}} = A_{2,\text{DC}} A_{\text{FB}} A_{\text{out2,DC}}, \tag{2.54}$$

$$= 31620 (90 \, \mathrm{dB}). \tag{2.55}$$

The cut-off frequency of the output stage must be high enough so that the closed-loop can remain stable.

$$f_{\text{out2}} \ge A_{\text{ol,ldo}} f_2, \tag{2.56}$$

$$\geq$$

316.2 MHz. (2.57)

In this case,  $f_{\text{out2}}$  with 632 MHz is chosen to emphasize stability.  $PSR_{2,\text{DC}}$  is relative relax as long as it is below 1. It can be seen that  $f_{\text{out2}}$  (632 MHz) is relatively crucial for the implementation.

In contrast, if  $\omega_{out2}$  is set to dominant pole, it should be low enough to prevent very high  $f_2$ . Assuming the error amplifier uses a simple differential pair, which has approximately 20 dB DC gain, the cut-off frequency of the error amplifier can be expressed by:

$$f_2 = \frac{BW}{A_{\text{FB}}A_{2,\text{DC}}},\tag{2.58}$$

$$= 3.16 \,\mathrm{MHz}.$$

(2.59)

Fig. 2.14 With the parameters of Table 2.3, the simulation results show achieved PSR  $-50 \, dB \, @ \, 100 \, kHz$ .

The overall open-loop gain can be calculated as  $A_{\rm ol,ldo}=100~(40~{\rm dB})$ . The cut-off frequency of output stage must be low enough for the closed-loop to remain stable.

$$f_{\text{out2}} \le \frac{f_2}{A_{\text{ol,ldo}}},\tag{2.60}$$

$$\leq 31.6 \,\text{kHz}.$$

(2.61)

In this case,  $f_{\rm out2}$  with 15.8 kHz is chosen to emphasize stability. Considering that the output stage usually generates a high current, an off-chip capacitor is usually required.

| Parameter                                                                     | $\omega_2$ dominant                                              | $\omega_{ m out2}$ dominant                                   |

|-------------------------------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------|

| $A_{2,\mathrm{DC}} \ PSR_{2,\mathrm{DC}} \ f_2\left(\omega_2/2\pi ight)$      | 60 dB<br>-6 dB<br>1 Hz                                           | 50 dB<br>-20 dB<br>191 MHz                                    |

| $A_{ m out2,DC}$ $PSR_{ m out2,DC}$ $f_{ m out2}$ ( $\omega_{ m out2}/2\pi$ ) | 20 dB<br>-50 dB<br>42 kHz                                        | 20 dB<br>20.4 dB<br>15 kHz                                    |

| PSR <sub>Ido,DC</sub> z <sub>2</sub> p <sub>2,1</sub> p <sub>2,2</sub>        | –66 dB<br>1.6 kHz<br>16.4 kHz<br>25.6 kHz                        | -50.5 dB<br>172.8 MHz<br>103.2 MHz<br>87.8 MHz                |

| Design constrains                                                             | Dedicated NMOS pass<br>transistor and charge<br>pump are needed. | Offchip cap and high bandwidth of error amplifier are needed. |

| Reference                                                                     | [30, 47, 88]                                                     | [27]                                                          |

Table 2.4 Design methodology comparison for full-spectrum PSR -50 dB [92]

The red font shows the absolute critical parameters, while the blue font and the black font represent less critical and relax parameters, respectively.

$A_{2,DC}$  with 20 dB can not reach DC PSR of -50 dB alone, so  $PSR_{2,DC}$  is used to further reduce the DC PSR according to the equation (2.14).

$$\left| \frac{PSR_{\text{out2,DC}}}{A_{\text{out2,DC}}} - PSR_{2,\text{DC}} \right| \le PSR_{\text{Ido,DC}} A_{2,\text{DC}} A_{\text{FB}}, \tag{2.62}$$

$$\leq 3.16 \times 10^{-2},\tag{2.63}$$

$$PSR_{2,DC} \in [1.02, 1.08].$$

(2.64)

The value of  $PSR_{2,DC}$  should be approximately 1, so that the same amount of interference on the gate and the source of the PMOS pass transistor can cancel each other out. Many state-of-the-art designs utilize this strategy, namely the

"feed-forward ripple cancellation technique". In this case,  $PSR_{2,DC}$  with 1.04 (0.34 dB) was chosen.

## **Full-spectrum PSR**

Table 2.4 shows two variants to achieve full-spectrum -50 dB PSR.

Fig. 2.15 With the parameters of Table 2.4, the simulation results show achieved full-spectrum PSR -50 dB.

If  $\omega_2$  is dominant, according the equation (2.29), the peak PSR decreases as  $PSR_{\text{out2,DC}}$  decreases.  $PSR_{\text{out2,DC}}$  can be set directly to  $-50 \, \text{dB}$ , while  $A_{2,\text{DC}}$  is set slightly higher than 50 dB and the other parameters are totally relax. To achieve a  $PSR_{\text{out2,DC}}$  of  $-50 \, \text{dB}$  without affecting  $A_{\text{out2,DC}}$ , the PMOS pass transistor is not sufficient. A NMOS pass transistor and a charge pump [46] can be utilized, since  $g_{\text{ds,N}}$  is naturally much smaller than  $g_{\text{m,N}}$ .

If  $\omega_{out2}$  is dominant, the off-chip capacitor should be also needed to pull  $f_{out2}$  to a low frequency.  $A_{2,DC}$  needs to be at least 50 dB to achieve a DC PSR of -50 dB. Therefore,  $f_2$  needs to be pushed to a high frequency, which is 191 MHz in this case.

# 2.4 Time-domain temperature sensor topology

# 2.4.1 Overview of voltage-domain temperature sensors

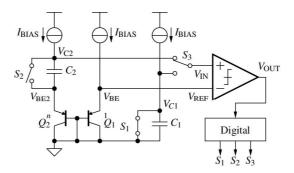

In order to achieve a low-power time-domain temperature sensing, the state-of-the-art voltage-domain concepts [31, 37, 5, 51] have to be studied. While many characteristics in CMOS are temperature dependent, the characteristic utilized to generate a voltage signal can be designed to generate a time signal as well. In CMOS the bipolar transistors are widely adopted to generate a proportional-to-absolute-temperature (PTAT) voltage and a temperature independent bandgap reference voltage.

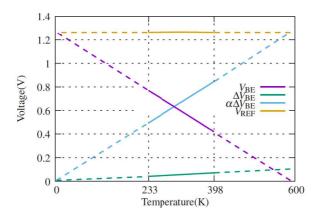

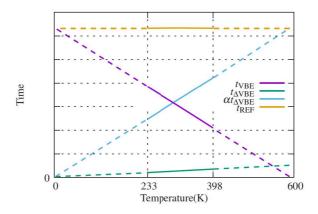

In Fig. 2.16 the diode-connected PNP transistors Q1 and Q2 are used to generate the base-emitter voltages  $V_{\rm BE1}$  and  $V_{\rm BE2}$ . The voltage difference  $\Delta V_{\rm BE}$  between  $V_{\rm BE1}$  and  $V_{\rm BE2}$  is amplified by the factor  $\alpha$  and produces the PTAT voltage  $\alpha \Delta V_{\rm BE}$ . The sum of  $V_{\rm BE1}$  and  $\alpha \Delta V_{\rm BE}$  is obtained as the reference bandgap voltage  $V_{\rm REF}$ . The analog-to-digital converter (ADC) converts the voltage  $\alpha \Delta V_{\rm BE}$  and produces the digital temperature code  $D_{\rm out}$ .

Fig. 2.16 Operational principle of the voltage-domain temperature sensor [31]

The base-emitter voltage of a bipolar transistor in the forward-active region can be written as:

$$V_{\rm BE} = \frac{kT}{q} \ln \left( \frac{I_{\rm C}}{I_{\rm S}} \right), \tag{2.65}$$

where k denotes Boltzmann's constant, q the elementary charge, and T absolute temperature in Kelvin,  $I_S$  the transistor's saturation current and the  $I_C$  the collector's current.

The transistor's saturation current can be written as [2]:

$$I_{\rm S} = bT^{4+m}e^{\frac{-E_g}{kT}},\tag{2.66}$$

where b is a proportional factor,  $m \approx -3/2$  and  $E_g \approx -1.2 \,\text{eV}$ .

The collector's current  $I_{\rm C}$  is held constant over temperature. Thus, the temperature coefficient of  $V_{\rm BE}$  can be written as:

$$\frac{\partial V_{\text{BE}}}{\partial T} = \frac{k}{q} \ln \left( \frac{I_{\text{C}}}{I_{\text{S}}} \right) - \frac{kT}{qI_{\text{S}}} \frac{\partial I_{\text{S}}}{\partial T}.$$

(2.67)

Finally, the coefficient of equation 2.67 can be expressed by [2]:

$$\frac{\partial V_{\text{BE}}}{\partial T} = \frac{V_{\text{BE}} - (4+m)V_T - E_g/q}{T}.$$

(2.68)

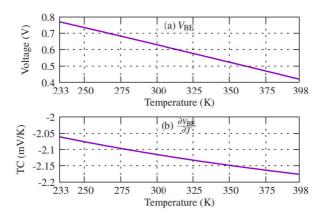

Equation 2.68 shows that the temperature coefficient of  $V_{BE}$  is dependent on the magnitude of  $V_{BE}$  itself. The value of  $\partial V_{BE}/\partial T$  is technology dependent.

If two bipolar transistors are biased with different currents, the difference of base-emitter voltages can be expressed by:

$$\Delta V_{\rm BE} = V_{\rm BE} - V_{\rm BE2} = \frac{kT}{q} \ln \left( \frac{I_{\rm C}}{I_{\rm C}/n} \right) = \frac{kT}{q} \ln(n), \tag{2.69}$$

where n is the ratio between two bipolar transistors (Fig. 2.16). The temperature coefficient can be easily expressed by:

$$\frac{\partial \Delta V_{\text{BE}}}{\partial T} = \frac{k}{q} \ln(n). \tag{2.70}$$

Obviously the temperature coefficient is PTAT.

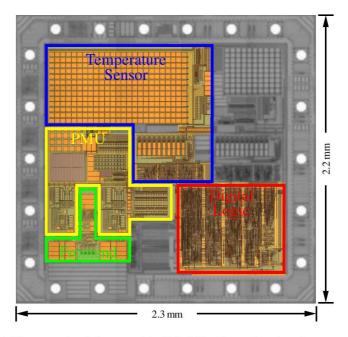

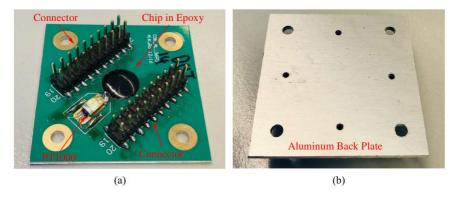

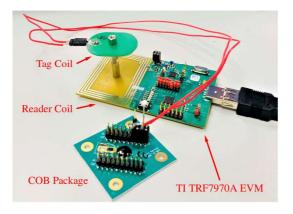

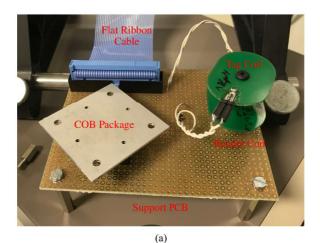

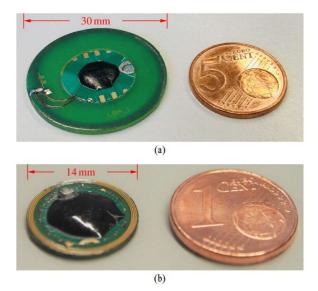

A bandgap reference voltage can be built based on  $V_{\rm BE}$  and  $\Delta V_{\rm BE}$ . The reference voltage is obtained by adding an amplified voltage of  $\Delta V_{\rm BE}$  to  $V_{\rm BE}$  and results in a temperature-independent voltage  $V_{\rm REF}$ :